Når design bliver mindre, hurtigere og mere komplekse, bliver det stadig mere udfordrende at sikre stabil signaltransmission og strømforsyning.

Som elektronikingeniør er det afgørende for dit designs ydeevne, at du forstår og håndterer signal- og strømintegritetsproblemer. Det kan være forskellen mellem et succesfuldt produkt og fejl under produktionen eller i brug.

Signaltransmission påvirkes af støj, krydstale eller elektromagnetisk interferens (EMI).

Strømforsyningen til komponenter er ustabil eller ineffektiv, hvilket fører til driftsproblemer.

Refleksioner og signalforsinkelser skaber problemer i højfrekvente kredsløb.

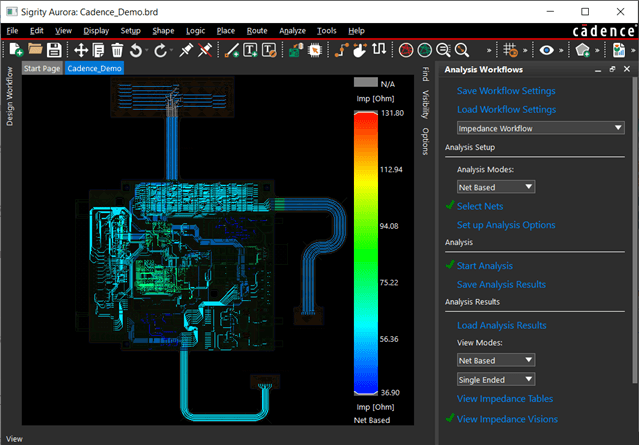

Det er udfordrende at minimere tab og sikre korrekt impedansmatching i designet.

Forsyningsspændingen svinger uacceptabelt på grund af spændingsfald eller transienter.

Designet kræver flere iterationer for at løse signal- eller strømrelaterede problemer, hvilket forsinker projekter og øger omkostningerne.

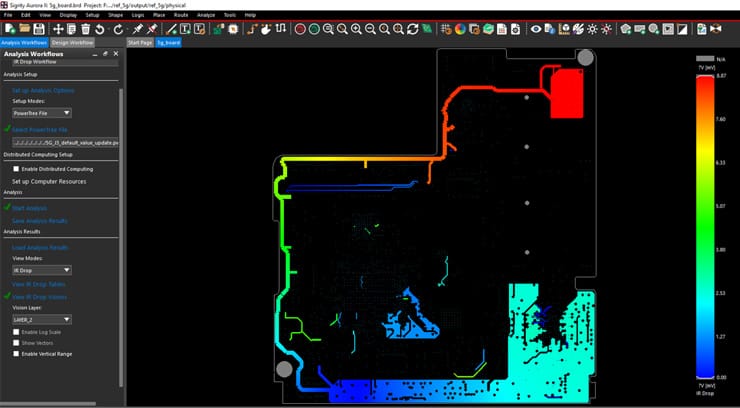

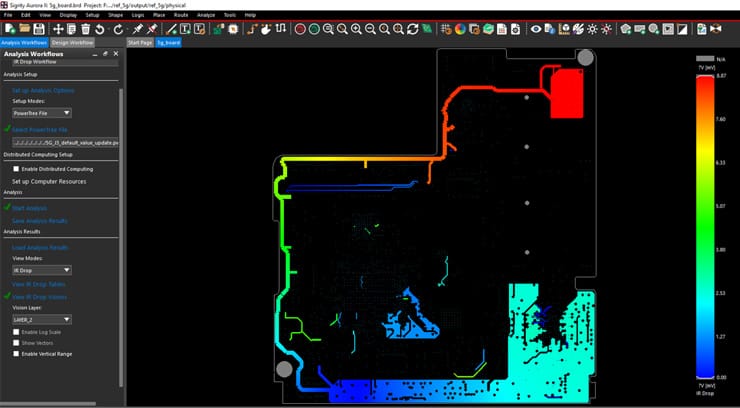

Med Cadence® Sigrity™ PowerDC™ får du øget nøjagtighed i den elektriske/termiske co-simulering samt sikkerhed for, at din PDN (Power Delivery Network) fungerer som forventet.

Med PowerDC kan du nemt finde utilsigtede spændingstab, høje strømtætheder, via med overdrevne strømme og termiske hotspots. Alle disse effekter kan i høj grad påvirke designets kvalitet og begrænse produktets levetid.

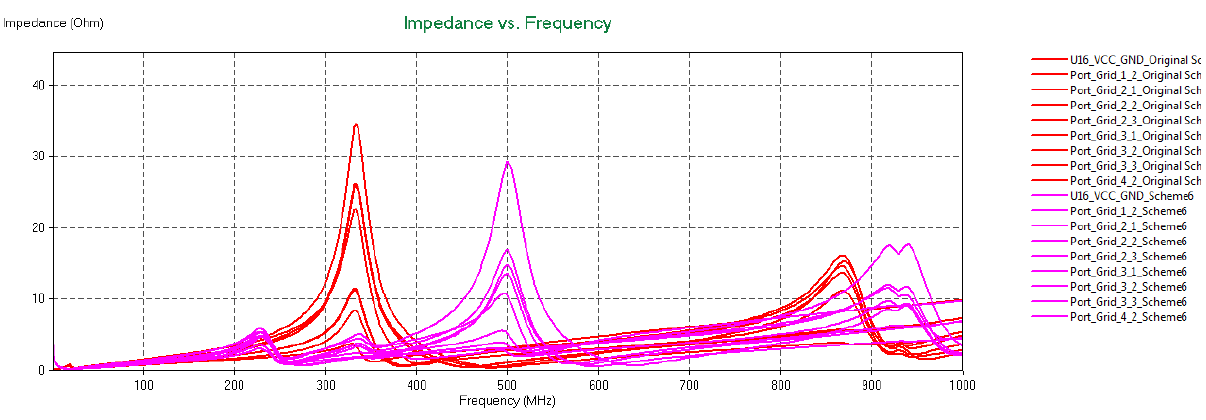

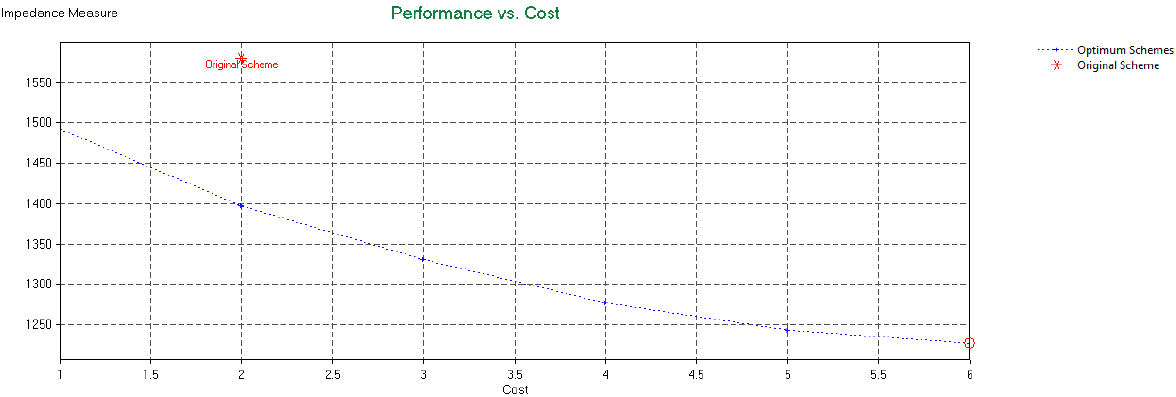

Med Cadence® Sigrity™ OptimizePI™ får du indsigt i, hvordan PDN frekvenskarateristikken ser ud for hver enkelt komponent - inklusiv planers udformning og placering i stackup, afkoblinger, deres routing og placering samt routing fra forsyningsplaner til komponenter. Der kan også optimeres på placerede afkoblinger mht. pris vs. performance og verificer EMI performance med måling af impedans for selvvalgte placeringer på layoutet.

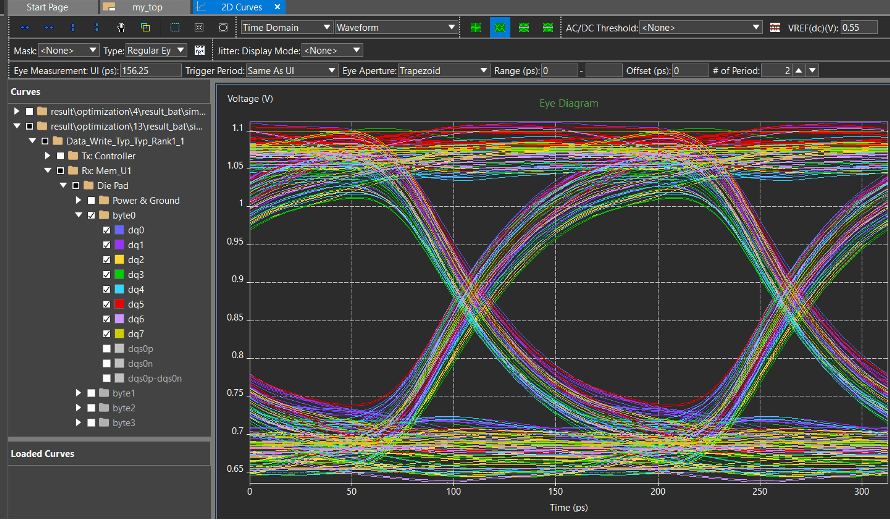

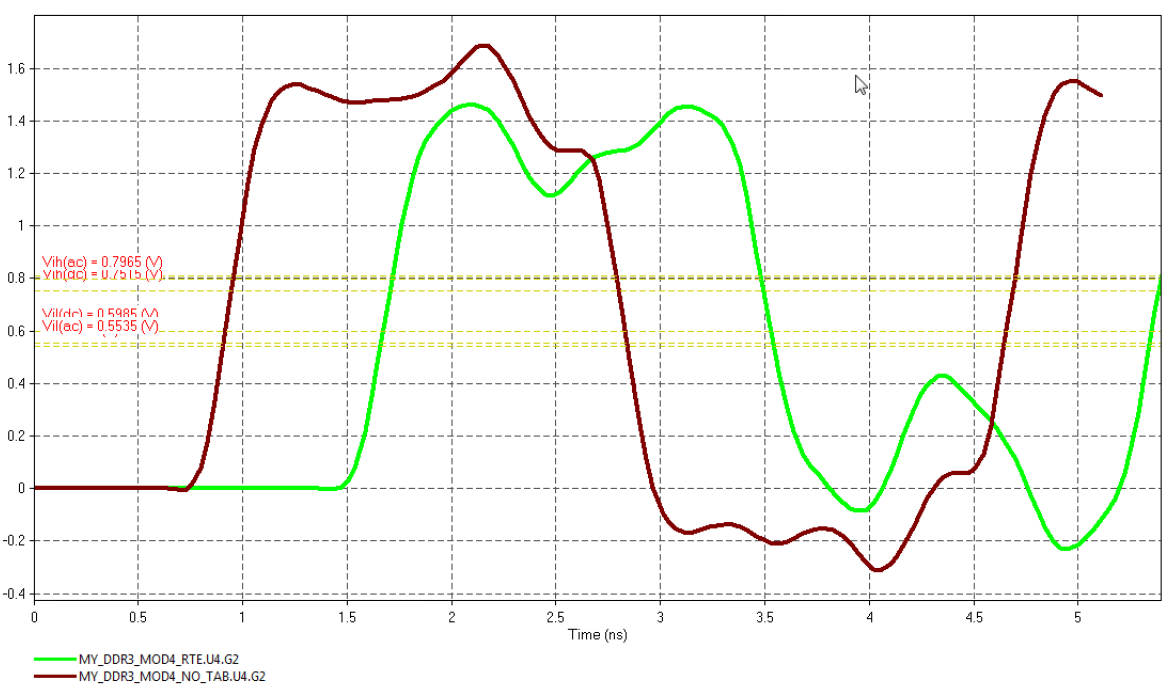

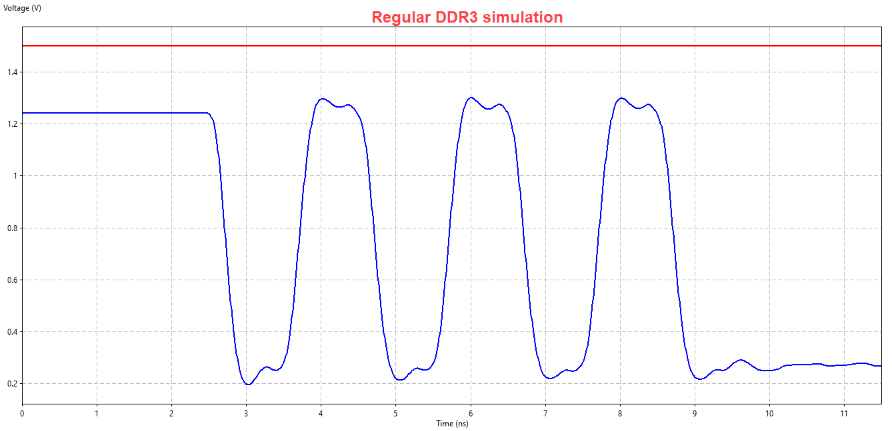

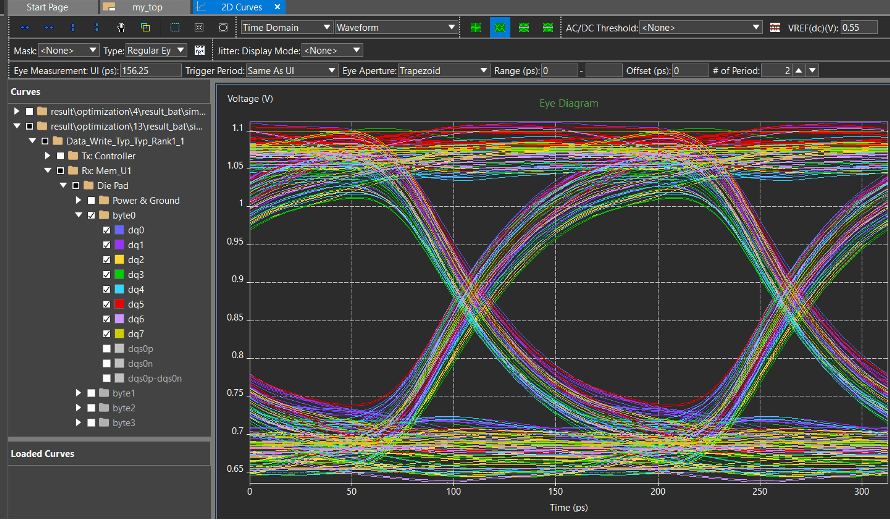

Simultaneous switching noise (SSN) kan ændre i timingen på et memory interface.

Med Sigrity™ Power-Aware SI får du en komplet løsning til analyse af source-synchronous interfaces, der anvendes til f.eks. DDR3- og DDR4 memory interfaces. Power-Aware SI omfatter både værktøjer til layout ekstraktion af baner og forsyninger, samt intuitive simuleringsværktøjer til parallel bus-analyse, der kan genere rapporter med information om tidsmargener bliver opfyldt i henhold til JEDEC standarden.

Udfør chip-til-chip analyse på highspeed SerDes interfaces, såsom PCI Express® (PCIe®), HDMI, SFP+, Xaui, Infiniband, SAS, SATA og USB med industristandard IBIS AMI-modeller.

Du kan køre pre-layout analyser ved hjælp af skabeloner og tilføje modeller af komponentpakker, stikforbindelser og layouts for at afspejle hele grænsefladen.

Kør simulationer for at identificere crosstalk-problemer og vise signalerne i grænsefladen, samt signalerne efter clock- og datagendannelse (CDR), som er beskrevet i IBIS AMI-modellen.

Ved at simulere den komplette grænseflade med millioner af bits kan den samlede bitfejlrate (BER) beregnes for at bestemme, om jitter- og støjniveauerne er inden for de specificerede tolerancer.