Udviklingen inden for elektronik har sat farten op i flere årtier, og det ser ikke ud til at sætte farten ned i fremtiden – tværtimod. I takt med at behovet for hurtigere, mere energieffektive og mindre enheder fortsat stiger, bliver udfordringerne med signal- og power-integritet også mere almindelige. Som elektronikingeniør/designer er det godt at kende faldgruberne – og endnu vigtigere, vide hvordan du løser dem.

Faldgruberne omhandler typisk:

- Karakteristisk impedans

- IR Drop

- Krydstale (Crosstalk)

- Returveje

- Loop induktans for afkoblingskondensatorer (Decoupling Capacitors)

Kendskabet til disse problemer og teorierne bag dem er bredt kendt i markedet, udfordringen er hvorledes de nemt kan identificeres og rettes tidligt i designprocessen for at undgå forsinkelser i din tidsplan og stressende fejlsøgningssessioner. Løsningen på disse udfordringer findes ved at bruge et værktøj som Sigrity.

Impedans og reflektioner

Mange interfaces stiller krav til styring af karakteristisk impedans for banerne. Hvis det ikke bliver gjort korrekt (på grund af f.eks. ukorrekt karakteristisk impedans eller dårligt designet baner), kan det resultere i en forringet signalintegritet. Det kan så resultere i lukning af øjediagrammet på grund af over- og undershoot. Impedans for baner bestemmes af stackup-geometri og materialespecifikationer. Parametre er listet nedenfor:

- Materialegenskaber (dielektrisk konstant)

- Geometri for baner (banebredde og tykkelse)

- Dielektrisk tykkelse (afstanden mellem bane og dens returplan)

- Transmissionslinjens topologi (f.eks. microstrip, stripline eller nedgravet microstrip med loddemaske)

Grunde til fejl vedr. karakteristisk impedans:

- Ændringer i stackup efter påbegyndt routing: Hvis et design er baseret på en bestemt banebredde for at opnå en ønsket karakteristisk impedans, og fabrikanten ændrer din stackup eller lagtykkelser efter routing er påbegyndt, kan dette føre til afvigelser.

- Forkerte impedansberegninger: Fabrikantens beregninger kan være unøjagtige. Det anbefales altid at gennemgå dokumentationen for stackup’en fra fabrikanten og dobbelttjekke impedanstabellen for at sikre korrektheden.

- Fejlagtig afstandsberegning i differential-par: Hvis designeren forveksler center-til-center-afstanden med kant-til-kant-afstanden i differential-par, kan det resultere i fejl i impedanskontrollen.

- Udeladelse af metaltykkelse eller loddemaske: Hvis beregninger ikke tager højde for banernes tykkelse eller tilstedeværelsen af loddemaske, kan det føre til afvigelser i impedansen.

Sådan optimerer du dit design:

- Arbejd sammen med din fabrikant og brug altid en field solver til at beregne banebredder.

- Vær sikker på at du router med den korrekte banebredde og afstand ved brug af regler.

- Vær opmærksom på huller og afgrænsninger i tilstødende planer, og sørg for at baner altid routes over en kontinuerlig returvej.

- Justér din stackup, hvis du ikke kan opnå en rimelig banebredde baseret på lagenes tykkelser. Måske har din stackup meget tynde lag på grund af et højt antal lag. Jo tyndere lagene er, desto smallere skal banerne være for at opnå den ønskede karakteristiske impedans. Derfor kan det være nødvendigt at justere din stackup for at opnå den impedans, du har brug for.

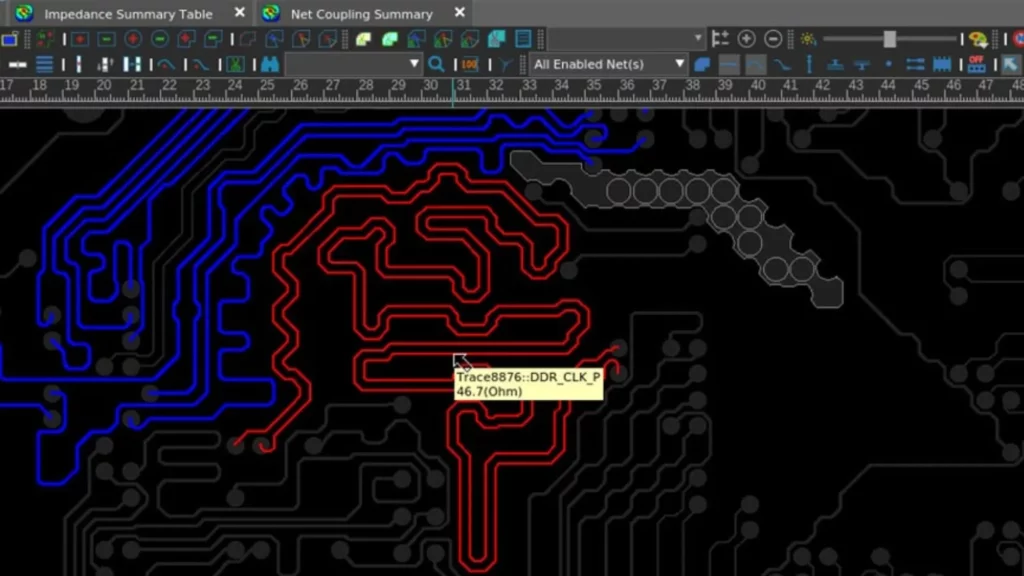

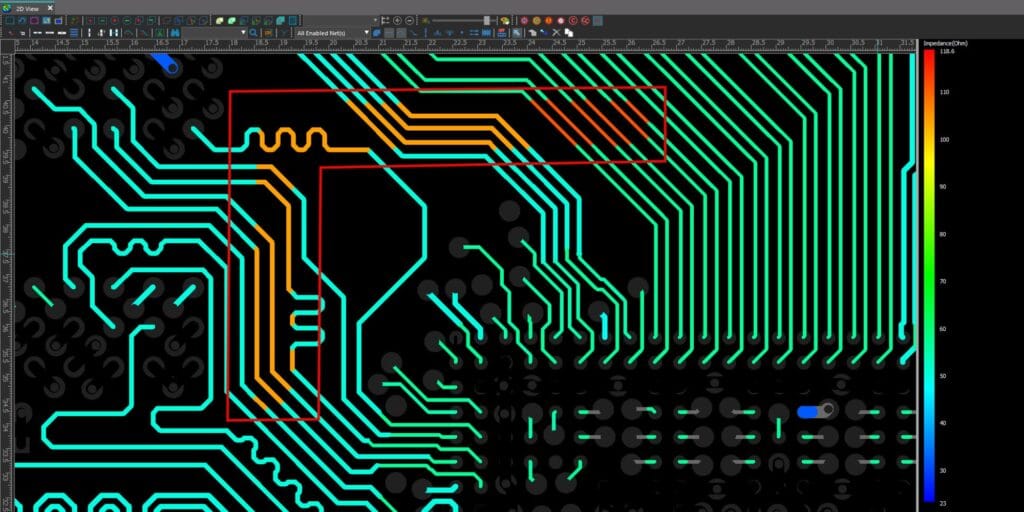

Der er også mulighed for grafisk farvekodning af baneimpedanser i Cadence Sigrity Starter Kit. Dermed kan du hurtigt finde de steder hvor impedansen ikke er som forventet.

IR Drop og stabilitet

Det refererer til spændingstabet langs en leder, når en jævnstrøm (DC) passerer gennem den. Dette tab skyldes lederens modstand, som forårsager en spændingsforskel mellem strømforsyningskilden og komponenterne. Aktive komponenter bliver ustabile fordi de oplever spændinger lavere end minimumsgrænserne for forsyningsspænding, fordi tabet er større end forventet. Oplever du et større spændingstab end forventet betyder også, at du reducerer den tilgængelige margin for eventuelle AC-ripple.

Grunde til fejl vedr. spændingstab:

- For tynde kobberlag anvendt i stackup’en, for tynde baner eller smalle kobberarealer anvendt på forsyningsnet.

- For få eller forkert placerede vias.

- Højere strømme og større spændingstab resulterer ofte også i yderligere øget spændingstab på grund af at resistansen af kobberet øges som funktion af kobbertemperaturen.

- Seriekomponenter som spoler, ferritter (ferrite beads) og sense modstande kan også bidrage til spændingsfald.

- Forkert placering af sense-modstand til feedback kan også resultere i at reguleringen ikke tager højde for spændingstab i strukturerne og derfor ikke regulerer korrekt.

Sådan optimerer du dit design:

- Om muligt, anvend tykkere kobber på forsyningsplaner men husk at det påvirker minimale størrelser for banebredde, baneafstand, annularringe, osv.

- Udnyt arealet på PCB’et og brug så brede planer/baner som muligt. Ved at øge tværsnitsarealet kan du reducere modstanden.

- Minimer afstanden mellem forsyning (VRM) og belastning (SINK). Dette vil ligeledes reducere modstanden.

- Bibehold så meget kobber som muligt ved at minimere størrelsen af via antipads. Vær opmærksom på din producents grænser for boring og kobberafstand.

- Til sidst, ved alle via-overgange bør du dobbelttjekke, at der er nok vias. Alternativt kan du f.eks. tilføje ekstra plating i vias for effektivt at reducere modstanden.

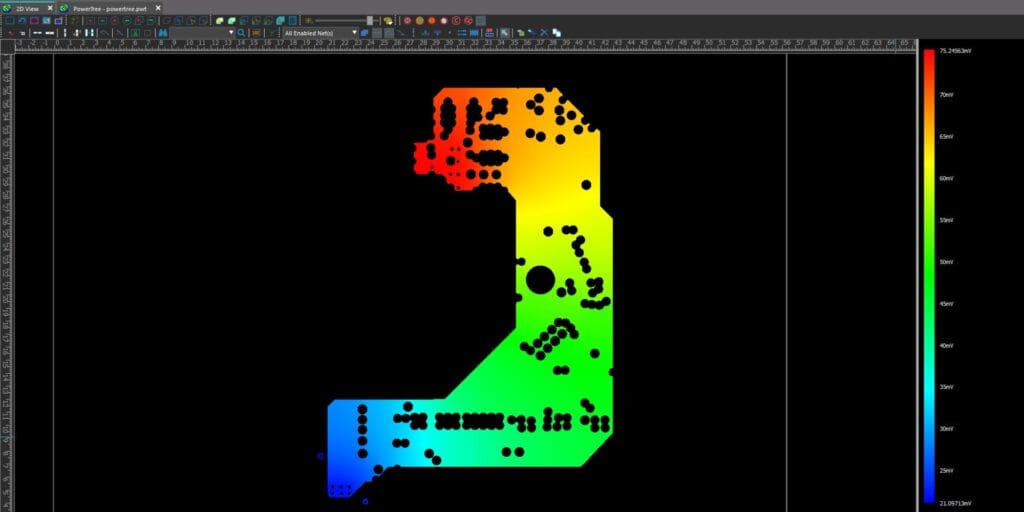

Cadence Sigrity Starter Kit tilbyder simulering og herefter farvekodning af layout så du nemt kan se det faktiske spændingstab, identificere hvor tabet opstår og i hvilke strukturer. I en simulation er det også klart nemmere at afprøve alternative materialer i stackup’en frem for nye print spin.

Kobling og Krydstale (Crosstalk)

Krydstale defineres som støj på et signal (victim) forårsaget af et andet forstyrrende signal (aggressor) på grund af elektrisk og magnetisk kobling mellem dem. Det kan i værste fald resultere i for høj eller for lav spænding for modtageren. Fra et designperspektiv er det målet at minimere koblingen mellem banerne og dermed minimere krydstalen.

Grunde til krydstale:

- For lille afstand mellem baner og dermed høj kobling mellem baner

- For lang afstand til referencelag (tykke laminater) medfører hørere kobling mellem baner i stedet for høj kobling til referencelag.

- Hurtige signalstignings- og faldtider påvirker krydstale, da den inducerede spænding er afhængig af dette.

- Ikke-ideel returvej og øger ligeledes krydstale.

- Flere signallag, der ligger direkte op ad hinanden, øger krydstale mellem signaler som er routet oven på hinanden.

Sådan optimerer du dit design:

- Definer regler for afstand mellem baner så tidligt i designforløbet som muligt. Brug gerne krydstalesimulering til at definere passende regler.

- Anvend så tynde laminater som muligt mellem signal- og referencelag, husk dog at tyndere laminater har indflydelse på banebreddefor impedansstyrede baner.

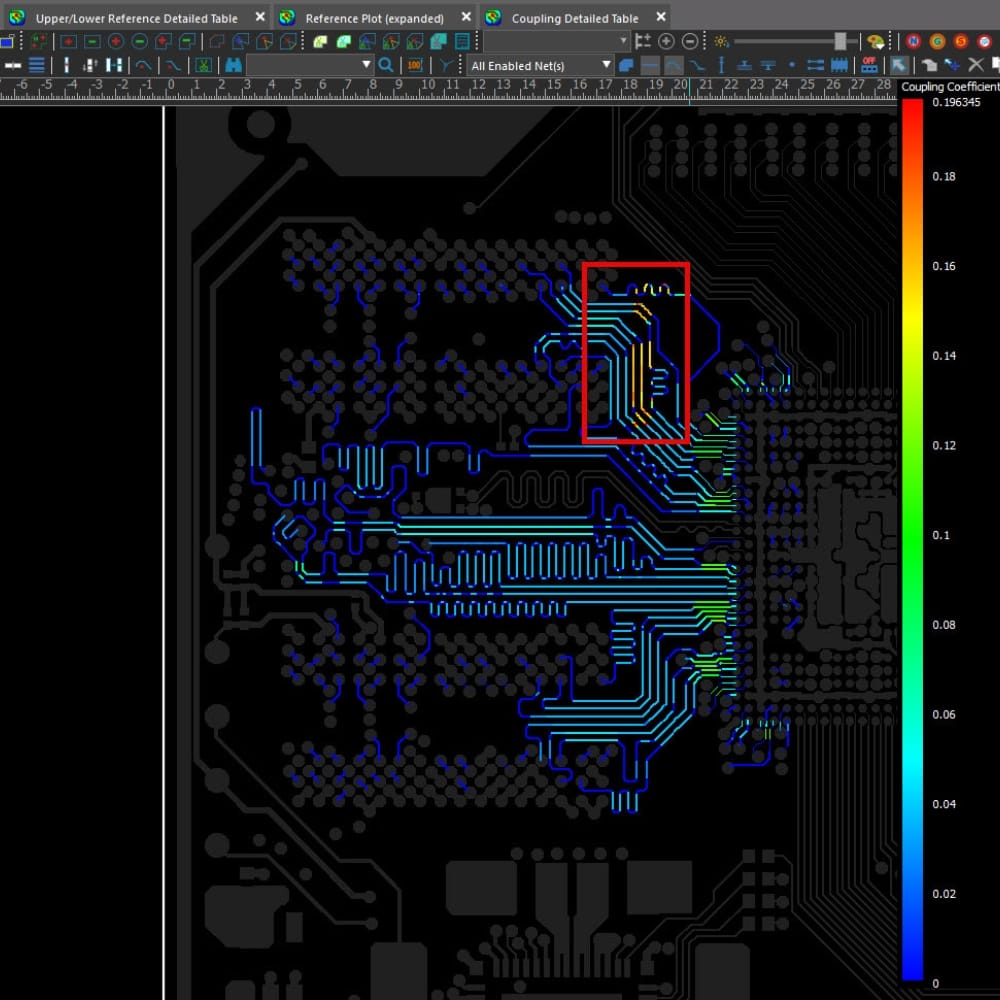

Har du to signallag i stackup’en der støder op til hinden kan routing ortogonalt på hinanden minimere krydstale. Er der mulighed for at konfigurere aktive kredse til at bruge langsommere falde- og stigetider, hjælper dette også. Cadence Sigrity Starter Kit kan ved hjælp af analyse beregne kobling mellem baner og farvekode layout så du nemt kan identificere steder hvor du har elementer der har høj kobling til hinanden.

Returveje

Kredsløbsteorien definerer at strøm kun kan løbe i en lukket kredsløb. I moderne designs er det let at følge signalet fra sender til modtager, men for at den kan det, skal der løbe en strøm tilbage fra modtager til sender. Ideelt set ønsker man som designer at designe en ”usynlig” returvej gennem planer og vias tilbage til senderen der er lige så god som vejen frem, men idet den er usynlig, gør den også svær at tjekke. Er der ikke styr på returvejen vil det vise sig som reflektioner og øget krydstale.

Grunde til fejl vedr. returveje:

- En af de mest almindelige fejl er at route en bane over diskontinuiteter i referencelag. Dette sker typisk, hvis du har flere power rails på samme lag i layoutet.

- En anden almindelig fejl er manglende returstrømsvia ved lagskifte: Når et signal skifter fra ét lag til et andet, bør der ideelt set placeres en retur-via i nærheden, så returstrømmen kan løbe gennem den.

- Overlappende antipads fra vias og komponentben kan også give problemer i returvejen for signalerne.

Sådan optimerer du dit design:

- Justér planer og baner for at bevare intakte referenceplaner.

- Tilføj vias til returstrøm ved lagskifte for signaler. I specielle situationer kan det give mening at simulere sig frem til ideel struktur med signal og returstrømsvias.

Med Cadence Sigrity Starter Kit kan du nemt via rapporter visualisere og finde de forbindelser hvor kræfterne skal bruges på review i stedet for at designere skal reviewe alt og måske ikke finde problemerne.

Afkoblingskondensatorer

Langt de fleste elektriske kredsløb har behov for afkoblingskondensatorer for at minimere AC ripple på forsyningerne og for at minimere EMI problemer. Der er flere forskellige former for afkoblingskondensatorer, men fælles for dem alle er at deres funktion er begrænset i frekvens af deres induktans. Induktansen for en afkobling er bestemt af flere ting såsom fysisk størrelse, intern opbygning, tilledning og lagopbygning.

Problemer med forsyningsnet og afkoblinger:

- Induktans tilføjet i med montering af afkoblinger begrænser funktionaliteten for afkoblingen og der skal derfor bruges flere for at opnå ønsket effekt.

- Lange tynde baner der forbinder afkoblingskondensatorer til forsyningsplaner, øger induktansen.

- Skal en afkoblingskondensator forbindes til planer på modsat side af placeringen øges induktansen ligeledes

- Fysisk store afkoblingskondensatorer har højere induktans end fysisk små kondensatorer.

Sådan optimerer du dit design:

- Brug Excel eller et af de andre gratis online værktøjer til at bestemme hvor mange afkoblinger du har behov for for at have et stabilt system.

- Design din stackup så du ved montering af afkobling får så lav en induktans som muligt.

- Placer og forbind afkoblinger med korte og brede forbindelser som muligt til forsyningsplaner så induktansen minimeres.

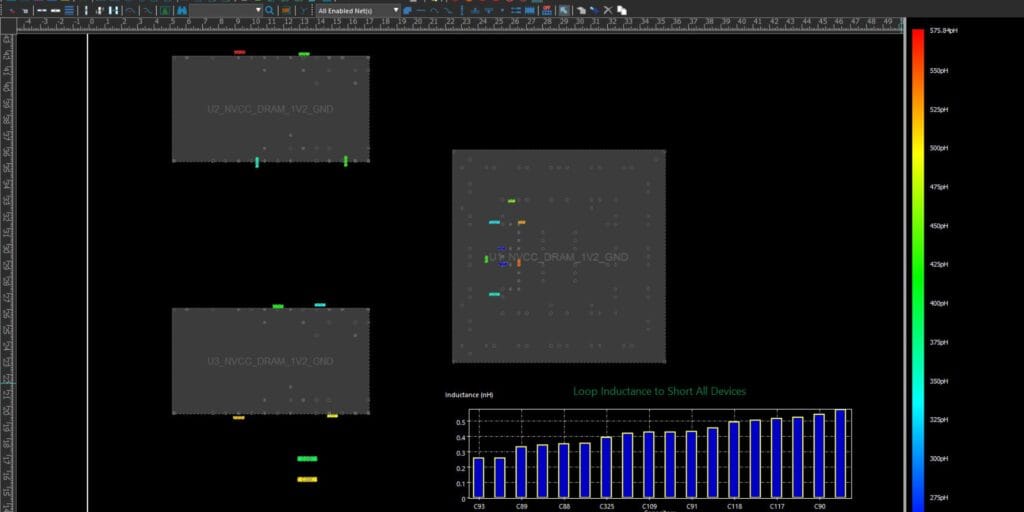

Med Cadence Sigrity Starter Kit kan du nemt ekstrahere loop induktans for alle afkoblinger og med farvekoder på layoutet identificere afkoblinger med ikke optimal tilledning.

Konklusion

Problemer med SI/PI er nemmest at løse før og under layout-fasen i din designproces. Med en grundig planlægning kan du minimere fejlene tidligt i processen, men tidspres kan ofte være en forhindring for at opnå denne ideelle arbejdsgang.

Med Cadence Sigrity Starter Kit kan du nemt i hele layoutfasen ved hjælp af analyser og intuitiv farvelægning have styr på faldgruber inden for signal- og power-integritet. Det betyder, at du sparer mere tid samt spilder mindre energi og færre ressourcer.